Design Compiler

Interface to DC

Design Vision(GUI)

$ design_vision -topographical_mode

DC Shell

$ dc_shell -topographical_mode

Batch mode

$ dc_shell -topo -f run.tcl | tee -i run.log

Workflow

$ cd workdir

$ dc_shell -topo

dc_shell-topo> read_verilog <verilog file>

dc_shell-topo> source <constraint file>

dc_shell-topo> check_timing

dc_shell-topo> set_app_var target_library <target library>

dc_shell-topo> compile_ultra

dc_shell-topo> write -format verilog -output <netlist.v>

dc_shell-topo> exit

Constraint report

$ cd workdir

$ dc_shell -topo

dc_shell-topo> read_verilog <netlist.v>

dc_shell-topo> source <constraint file>

dc_shell-topo> set_app_var target_library [list <target library>]

dc_shell-topo> report_constraint -all_violators

dc_shell-topo> exit

Add file search path

# set_app_var search_path "$search_path rtl cons libs"

dc_shell-topo> set_app_var search_path [list . $search_path <serch path>]

Library

dc_shell-topo> set_app_var target_library [list <target library>]

dc_shell-topo> set_app_var link_library [list * $target_library IP.db]

dc_shell-topo> set_app_var symbol_library "* target.db IP.db"

Set current design

dc_shell-topo> read_verilog [list A.v B.v Top.v]

dc_shell-topo> current_design MY_TOP

dc_shell-topo> link

Check design

check_design checks your current design for connectivity and hierarchy issues

dc_shell-topo> read_verilog {A.v B.v Top.v}

dc_shell-topo> current_design MY_TOP

dc_shell-topo> link

dc_shell-topo> check_design

## html format output

dc_shell-topo> check_design -html check_design.html

Load design by analyze and elaborate

dc_shell-topo> analyze -format verilog [list A.v Top.v]

dc_shell-topo> elaborate MY_TOP -parameters "A_WIDTH=9, B_WIDTH=16"

Load design form directory

dc_shell-topo> read_file [list $RTL_PATH] -autoread -recursive -format verilog -top MyTopModule

Save the ddc design before compile

$ cd workdir

$ dc_shell -topo

dc_shell-topo> read_verilog <verilog file>

dc_shell-topo> current_design MY_TOP

dc_shell-topo> link

dc_shell-topo> check_design

dc_shell-topo> write -format ddc -hier -output unmaped/MY_TOP.ddc

dc_shell-topo> source <constraint file>

dc_shell-topo> check_timing

dc_shell-topo> set_app_var target_library [list <target library>]

dc_shell-topo> compile_ultra

Save the ddc design after compile

dc_shell-topo> compile_ultra

dc_shell-topo> change_names -rule verilog -hier

dc_shell-topo> write -format verilog -hier -output netlist.v

dc_shell-topo> write -format ddc -hier -output maped/MY_TOP.ddc

Timing Constraints

Create Clock

create_clock -period 2 [get_ports clk]

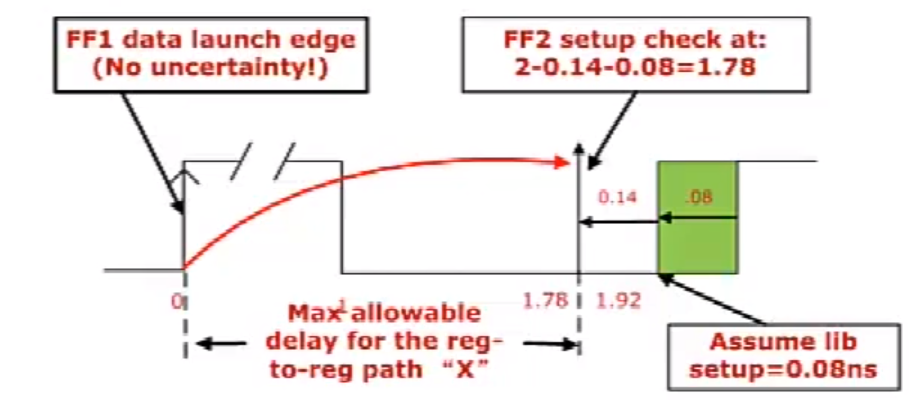

Setup Time

set_clock_uncertainty -setup 0.14 [get_clocks clk]

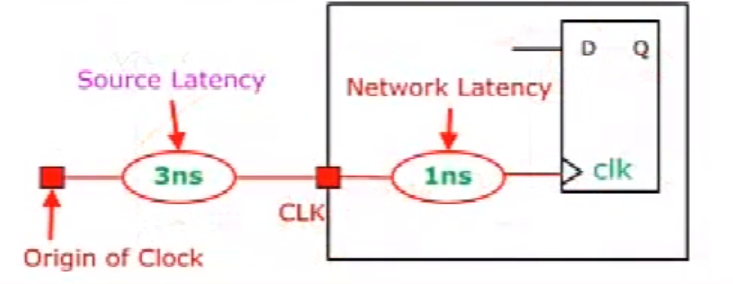

Model latency or insertion delay

set_clock_latency -source -max 3 [get_clocks clk]

set_clock_latency -max 1 [get_clocks clk]

Model Transition Time

Transition models the rise and fall time of the clock waveform at the register clock pins

set_clock_transition 0.08 [get_clocks clk]

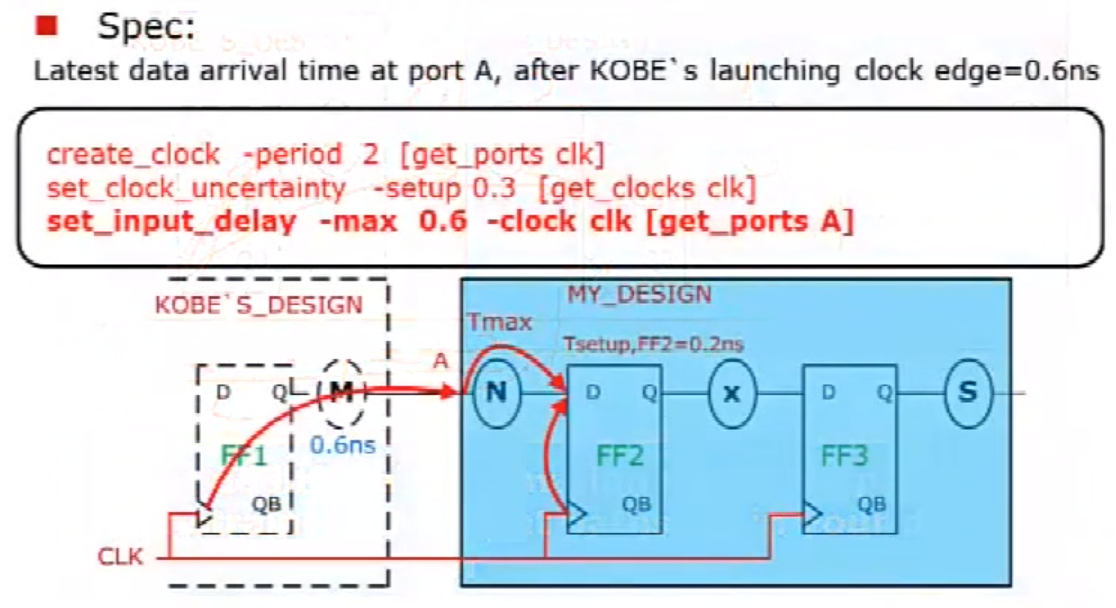

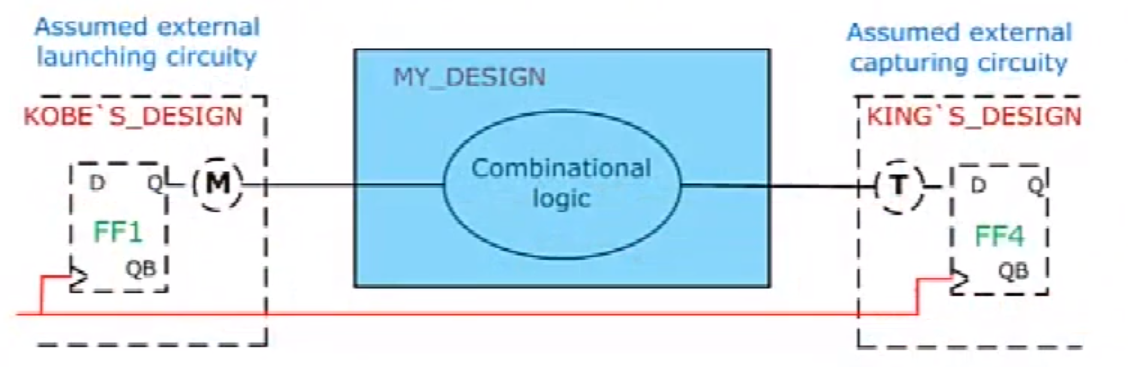

Constraining input paths

set_input_delay -max 0.6 -clock clk [get_ports A]

To constraining all inputs the same, except for the clock port

set_input_delay -max 0.5 -clock clk [remove_from_collection [all_inputs] [get_ports clk]]

To remove the constrain of a port

remove_input_delay [get_ports clk]

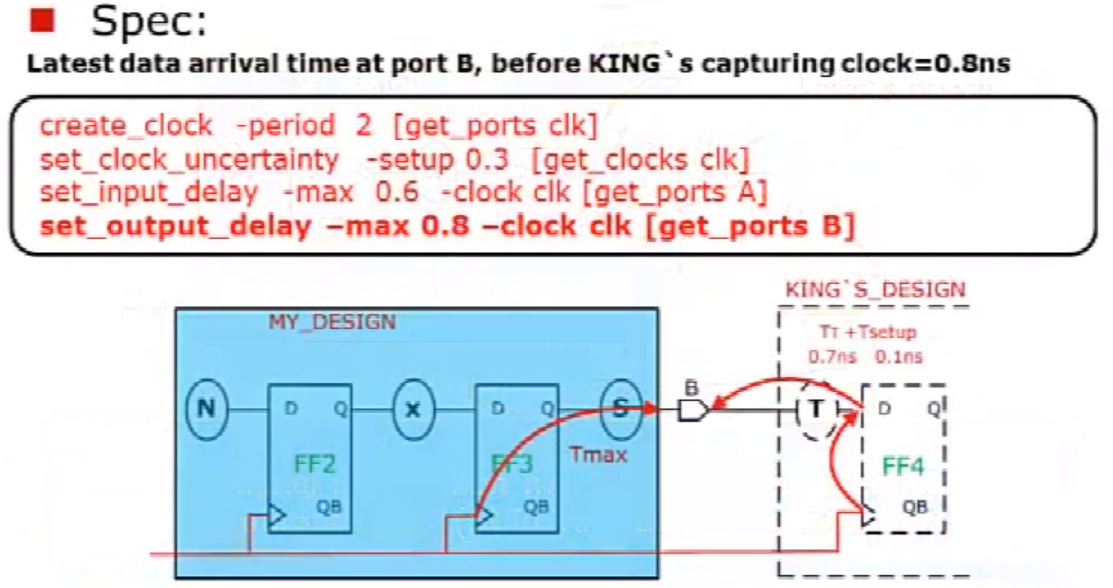

Constraining output paths

set_output_delay -max 0.8 -clock clk [get_ports B]

To constraining all outputs the same

set_output_delay -max 0.5 -clock clk [all_outputs]

Constraining a pure combinational design

we should create a virtual clock

create_clock -name vclk -period 2

Constraining clk to q

set_clk_to_q_max 1.5

set_clk_to_q_min 0.9